KAIST 연구진이 PIM(Processing-In-Memory) 반도체의 성능을 향상시키는 새로운 네트워크 구조를 개발했다.

KAIST 전기·전자공학부 김동준 교수 연구팀은 미국 노스이스턴·보스턴대학, 스페인 무르시아대학 연구진과 협력해 PIM 반도체 간 집합통신에 특화된 '인터커넥션 네트워크 아키텍처'를 개발했다고 19일 밝혔다.

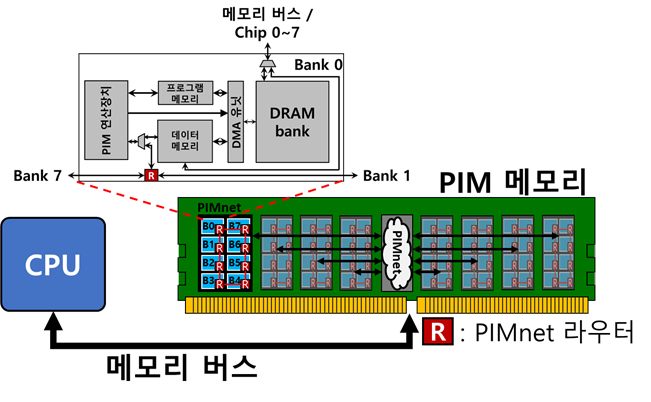

연구는 PIM 반도체 내 연산장치 간 데이터 이동 과정에서 발생하는 병목현상 해결, CPU 개입을 최소화해 전반적인 시스템 성능을 개선하는 것이 핵심이다.

연구팀은 기존 PIM 반도체가 메모리 내부 버스를 통해 데이터를 이동시키는 방식을 넘어, 연산장치들을 직접 연결하는 인터커넥션 네트워크 구조를 적용했다. 이를 통해 PIM 반도체의 대역폭 활용률을 극대화하고 확장성을 높였다.

PIM 반도체는 메모리 내부에서 직접 연산을 수행해 데이터 이동을 최소화하는 기술이지만 기존 구조에서는 연산장치 간 통신이 원활하지 않아 성능이 제한됐다. 특히 데이터를 주고받을 때 CPU를 거쳐야만 했기 때문에 처리 속도가 느려지는 문제가 있었다.

연구팀이 개발한 새로운 네트워크 구조는 이러한 한계를 극복하고, PIM 반도체의 독립적인 데이터 통신을 가능하게 했다.

연구진에 따르면 새로운 구조를 적용한 PIM 반도체는 기존 대비 최대 11배의 성능 향상을 보였다.

김동준 교수는 "PIM 컴퓨팅 시스템은 성능·효율은 좋지만 연상장치가 데이터 이동으로 확장성 제한이 있었다"며 "인터커넥트가 제한을 늘리는 해법이 될 수 있다"고 말했다.